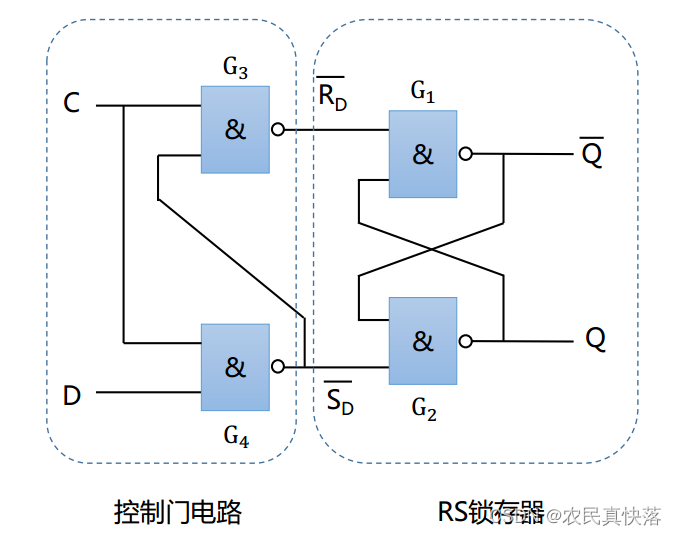

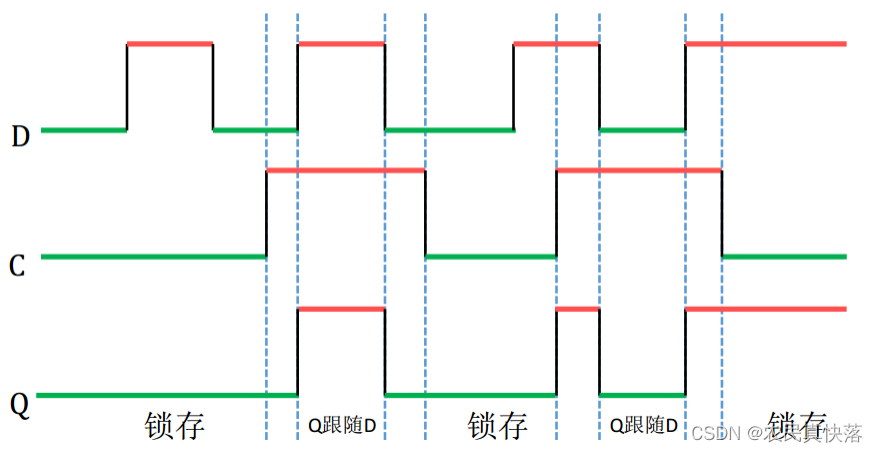

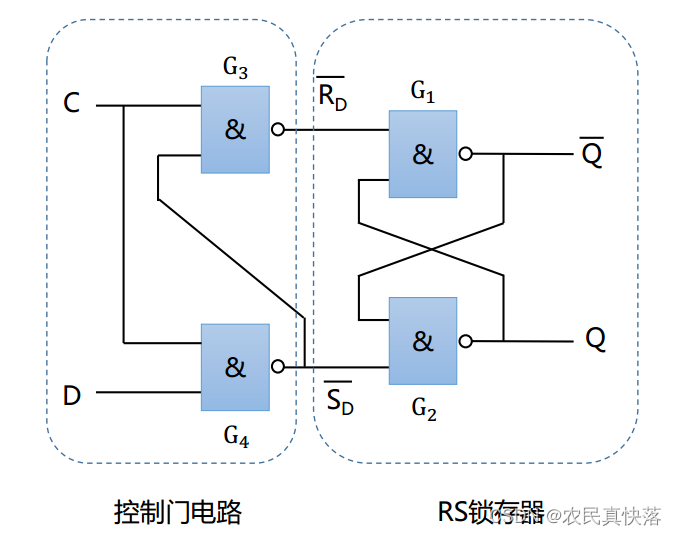

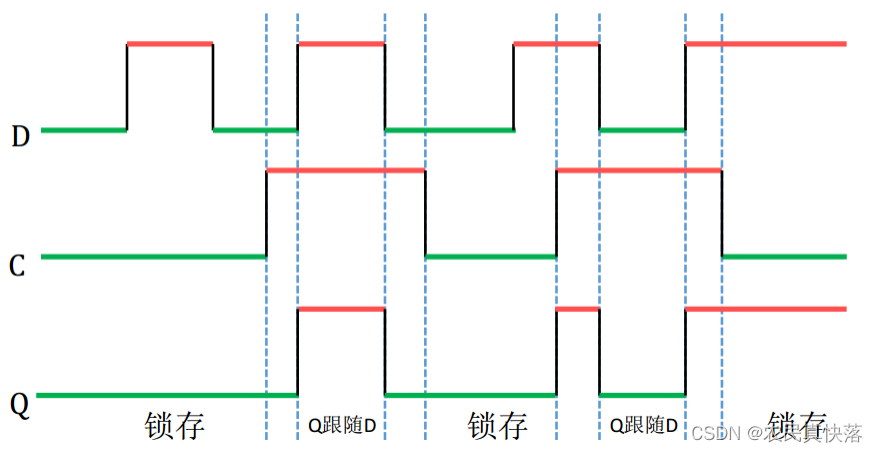

锁存器原理

- 当控制信号 C=0 时,Q维持不变

根据与非门的逻辑定律,无论 D 输入什么信号,RD 和 SD 信号同时为 1。根据由与非门组成的 RS 锁存器的逻辑定律,RD 和 SD 都同时 等于 1 的话,锁存器的输出端 Q 将维持原状态不变。

- 当控制信号 C=1 时,Q由D来决定

- 如果此时 D=0,SD 就等于1,RD 就等于 0,根据 RS 锁存器的逻辑规律,电路的结果就为 0 状态;

- 如果 D =1,那么 RD 就等于 1,SD 也就等于 0,锁存器的结果就为 1 状态。

也就是说,此时锁存器的状态是由激励输入端 D 来确定的,

并且 D 等于什么,锁存器的状态就是什么,这就是我们前面所说的,将单路数据 D 存入到锁存器之中。

在绝大多数设计中我们要避免产生锁存器。它会让您设计的时序出问题,并且它的隐蔽性很强,新人很难查出问题。锁存器最大的危害在于不能过滤毛刺和影响工具进行时序分析。这对于下一级电路是极其危险的。所以,只要能用触发器的地方,就不用锁存器。

if语句

if语句不带else

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

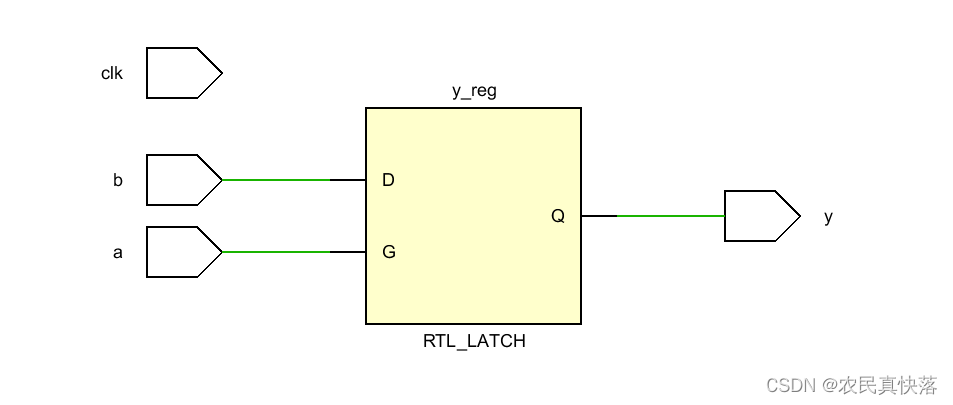

| `timescale 1ns / 1ps

module latch

(

clk,

a,

b,

y

);

input clk;

input a;

input b;

output reg y;

always @(*) begin

if( a == 1)

y = b;

end

endmodule

|

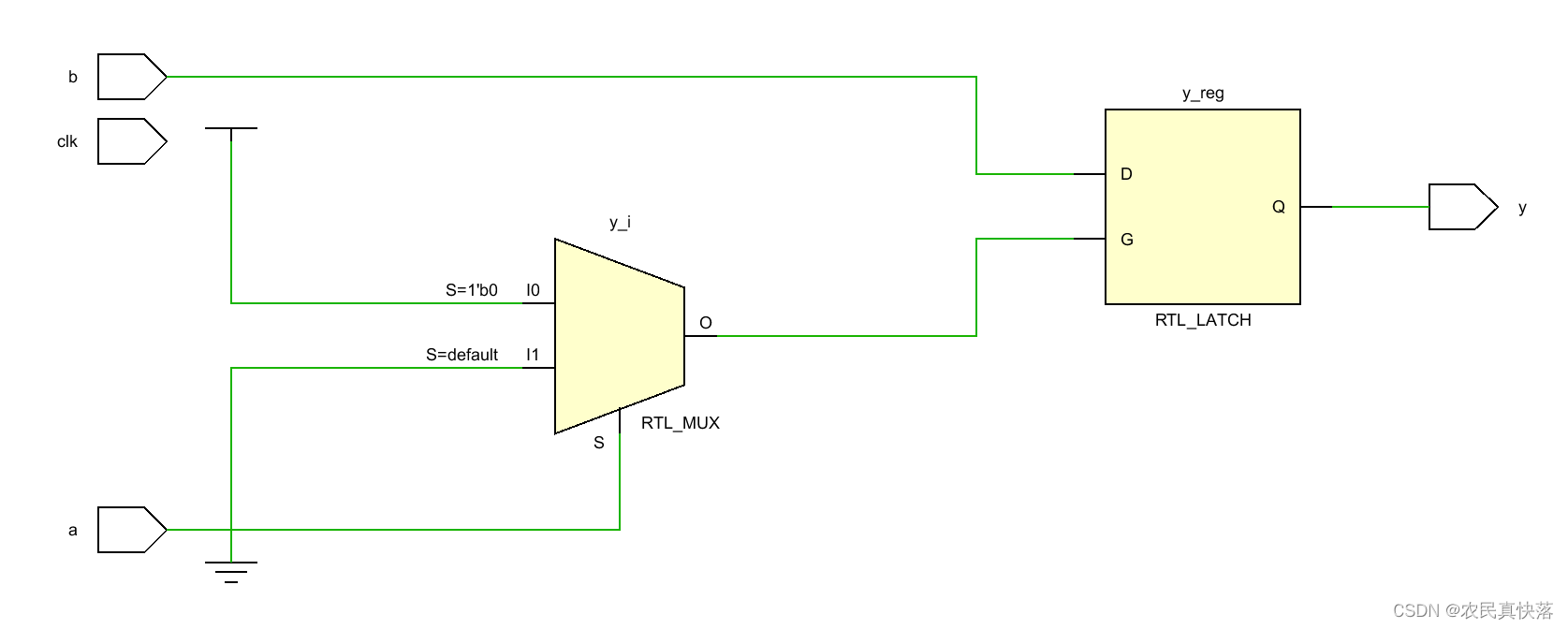

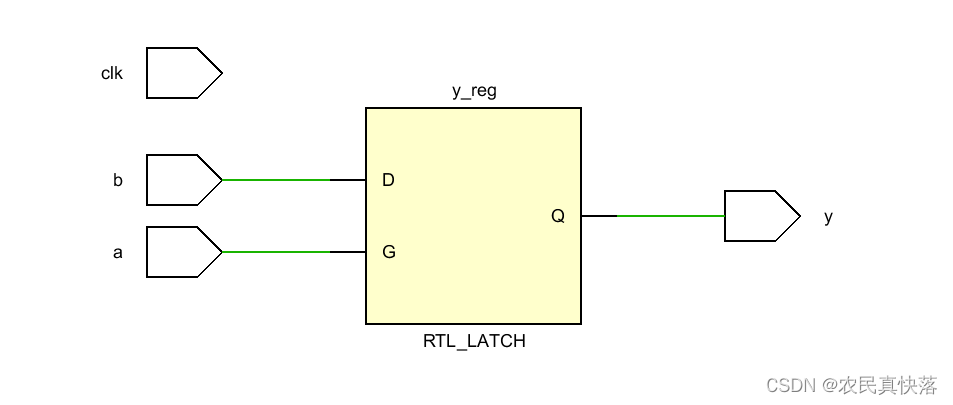

if语句不带else 对应 RTL原理图

if语句带else

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

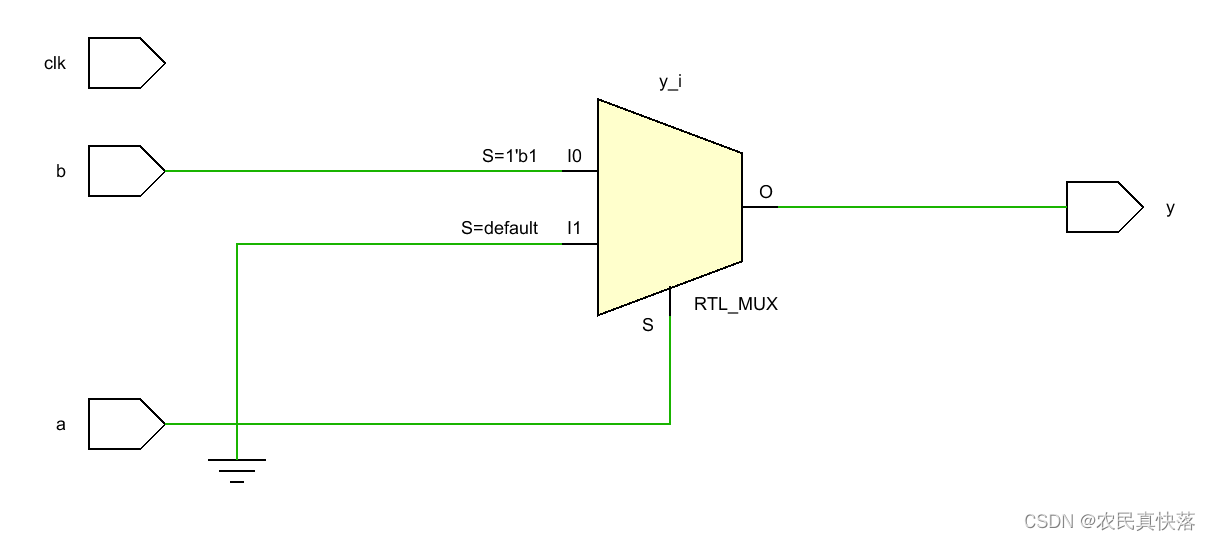

| `timescale 1ns / 1ps

module latch

(

clk,

a,

b,

y

);

input clk;

input a;

input b;

output reg y;

always @(*) begin

if( a == 1)

y = b;

else

y = 0;

end

endmodule

|

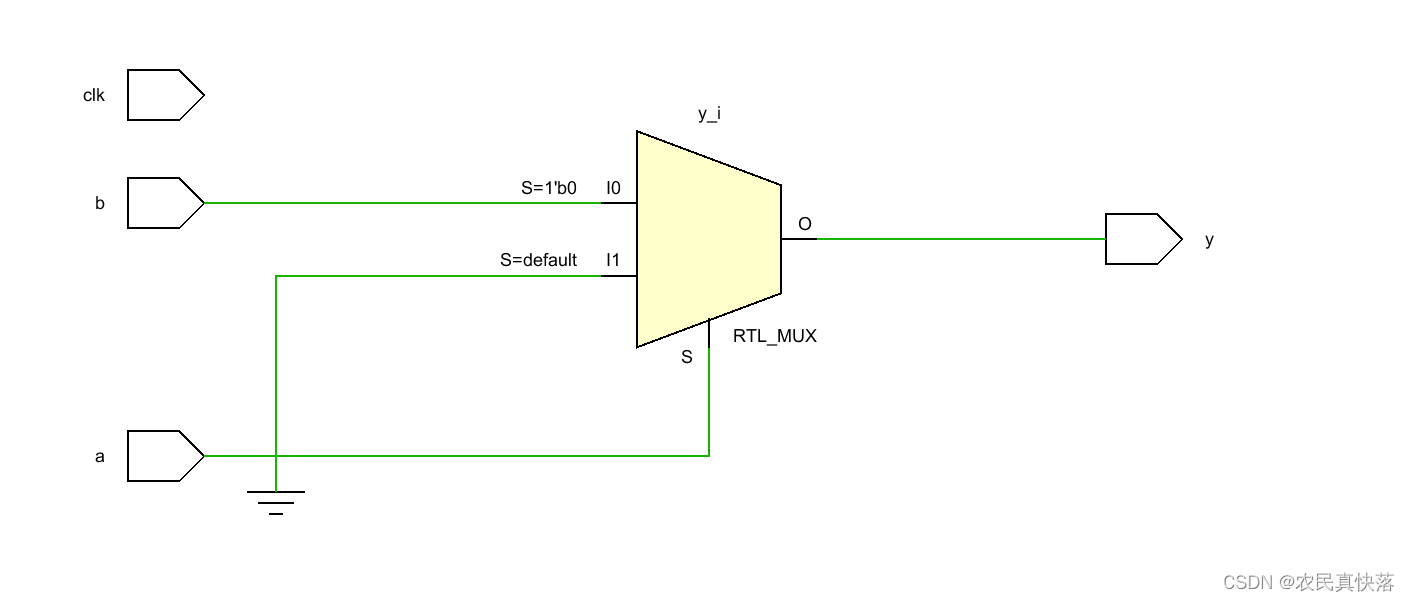

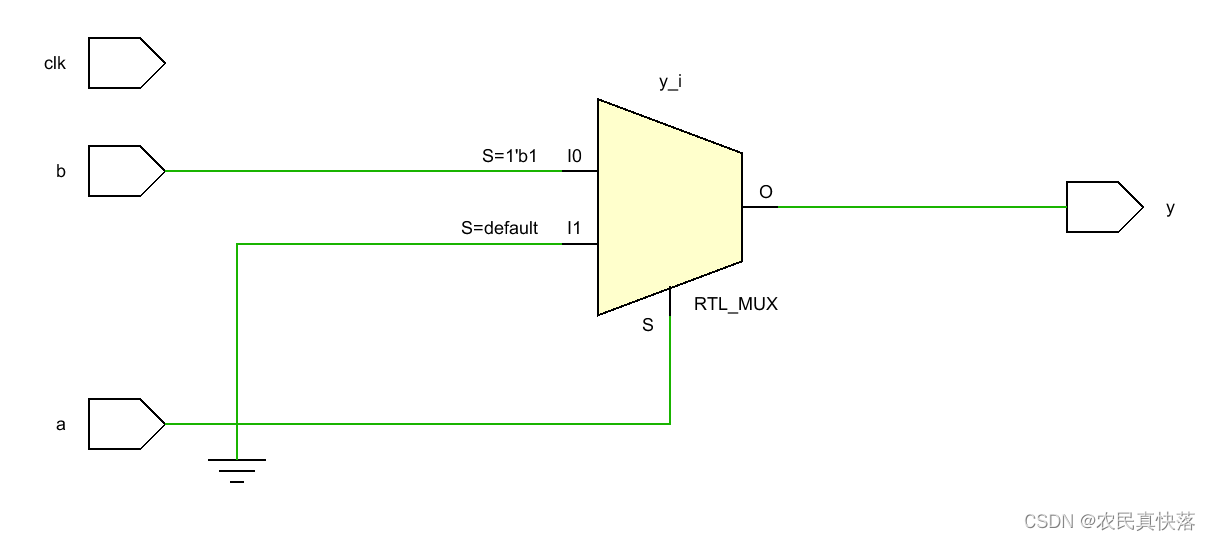

if语句带else 对应 RTL原理图

if语句带else 对应 RTL原理图

Case语句

Case语句不带feault

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

| `timescale 1ns / 1ps

module latch

(

clk,

a,

b,

y

);

input clk;

input a;

input b;

output reg y;

always @(*) begin

case(a)

0 : y = b;

endcase

end

endmodule

|

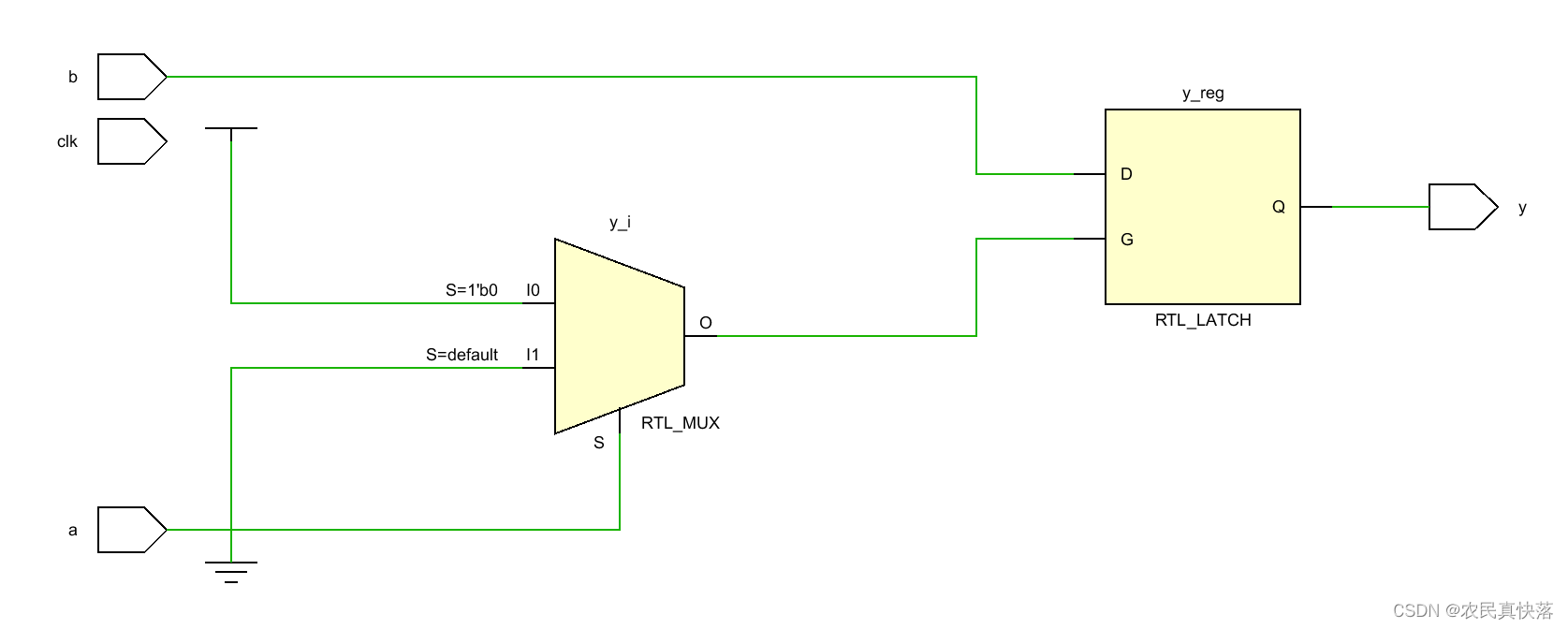

Case语句不带feault 对应 RTL原理图

Case语句带default

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

| `timescale 1ns / 1ps

module latch

(

clk,

a,

b,

y

);

input clk;

input a;

input b;

output reg y;

always @(*) begin

case(a)

0 : y = b;

default : y = 0;

endcase

end

endmodule

|

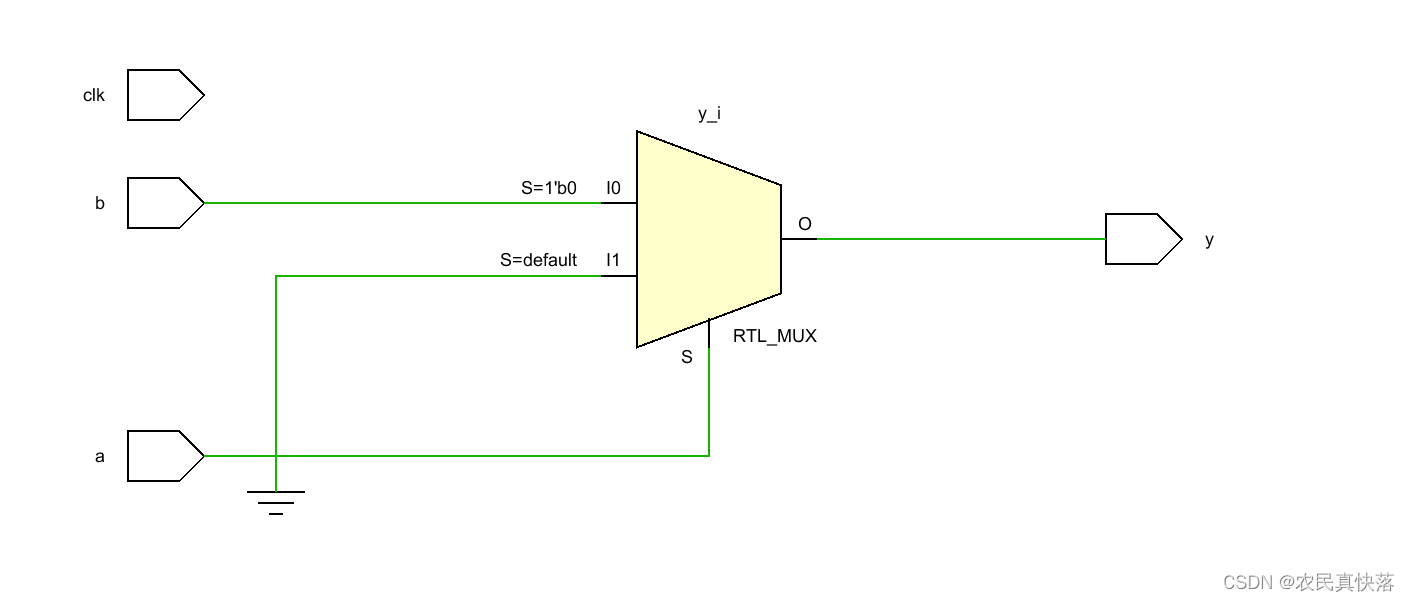

Case语句不带feault 对应 RTL原理图

参考资料

- 正点原子逻辑设计

- B站 花几分钟理解锁存器

- 锁存器与触发器详解1 SR锁存器